A leading semiconductor design company

With operational hubs in the USA, Canada, Bangladesh, and India, our global reach ensures seamless service delivery.

01

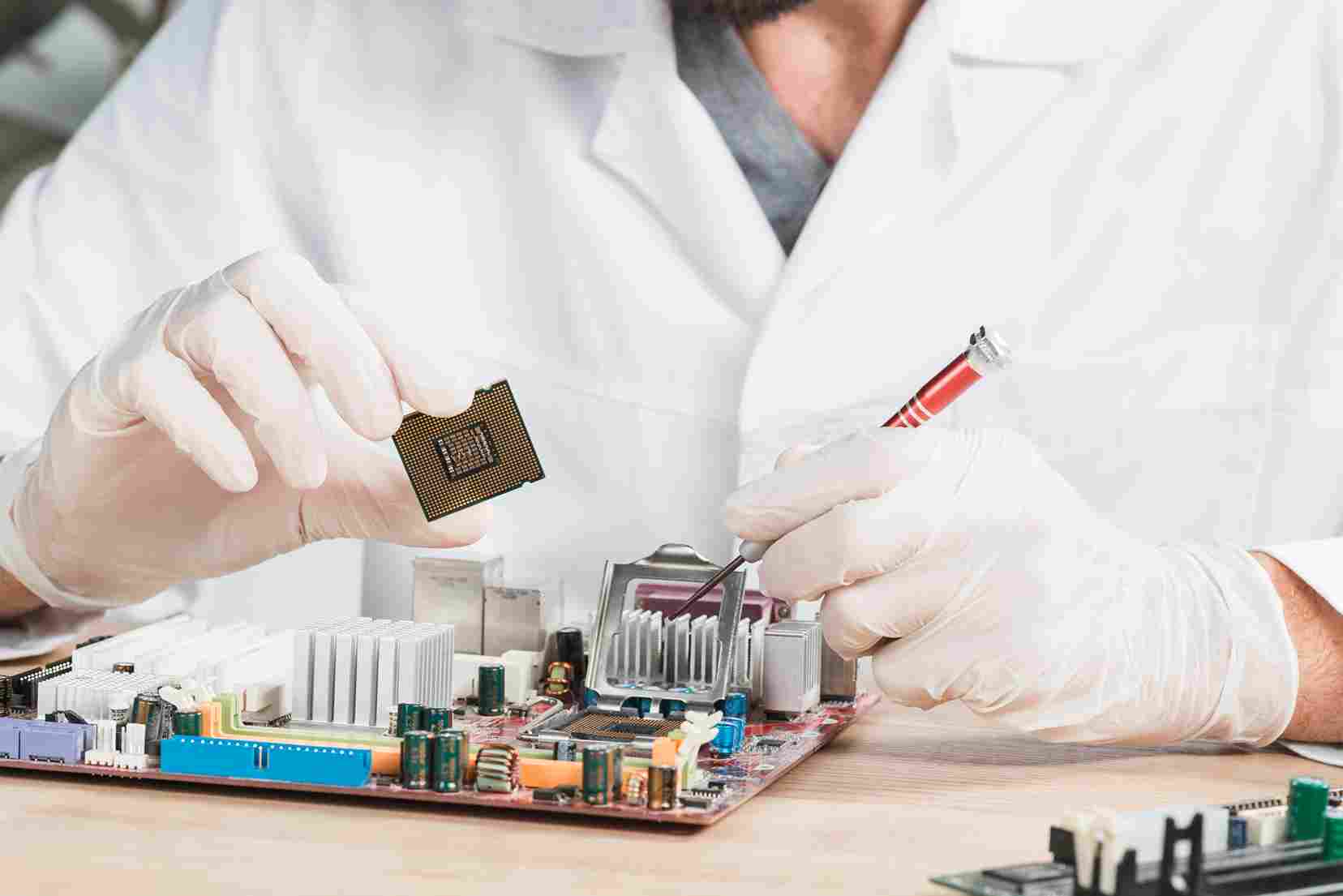

Cutting Edge Expertise

The majority of our engineers are working below 20 nm technologies

02

Diverse Customer Base

More than 20 concurrent customers from semiconductor (digital/analog) companies, IP developers, and state-of-the-art foundries to high-quality technology start-ups.

03

Competitive Value

Our high quality design services consistently exceed customer expectations on performance and price.

04

TSMC DCA Partner

Since 2021, ULKASEMI has been a member of TSMC’s Design Center Alliance.

05

ISO 9001:2015 Certification

Our largest design center in Dhaka, Bangladesh is ISO 9001:2015 certified for an effective quality management system.

06

ISO 27001:2022 Certification

Our largest design center in Dhaka, Bangladesh is ISO 27001:2022 certified for an information security management system.

View all

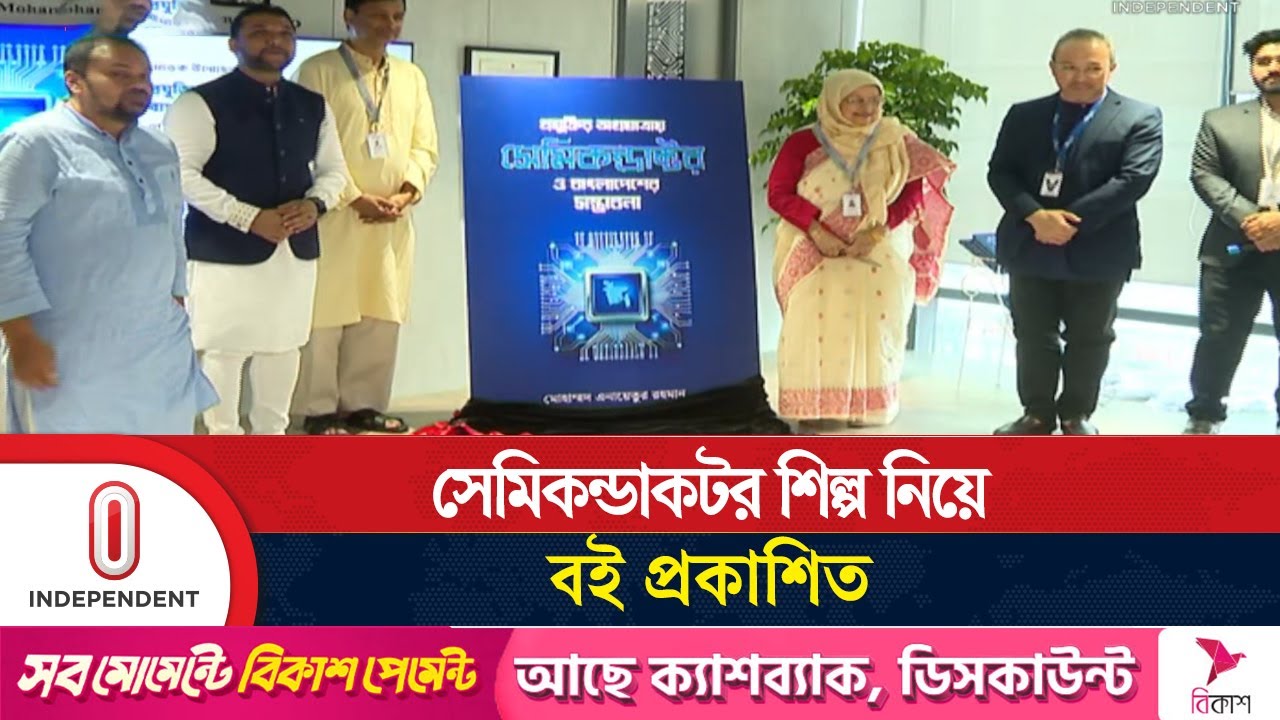

3 weeks ago

ULKASEMI CEO Mohammed Ena...

Mohammed Enayetur Rahman, CEO and President of ULKASEMI, has...

1 month ago

ULKASEMI Wins HSBC Export...

ULKASEMI has been honored with the HSBC Export Excellence Aw...